본 정리는 CS422-컴퓨터 구조 및 설계 : 하드웨어/소프트웨어 인터페이스. David A. Patterson, 존 헤네시 책을 바탕으로 하고 있음을 미리 알립니다.

MIPS Pipelined Datapath

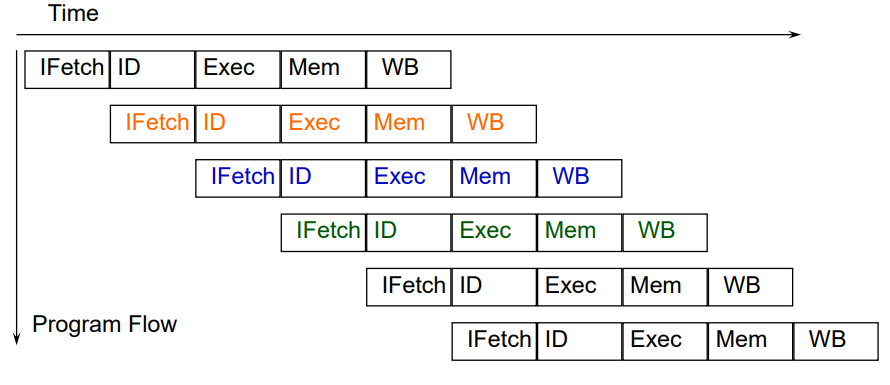

MIPS의 파이프라인은 다음의 5가지 stage를 갖는다.

- IF: Instruction fetch from memory

- ID: Instruction decode & register read

- EX: Execute operation or calculate address

- MEM: Access memory operand

- WB: Write result back to register

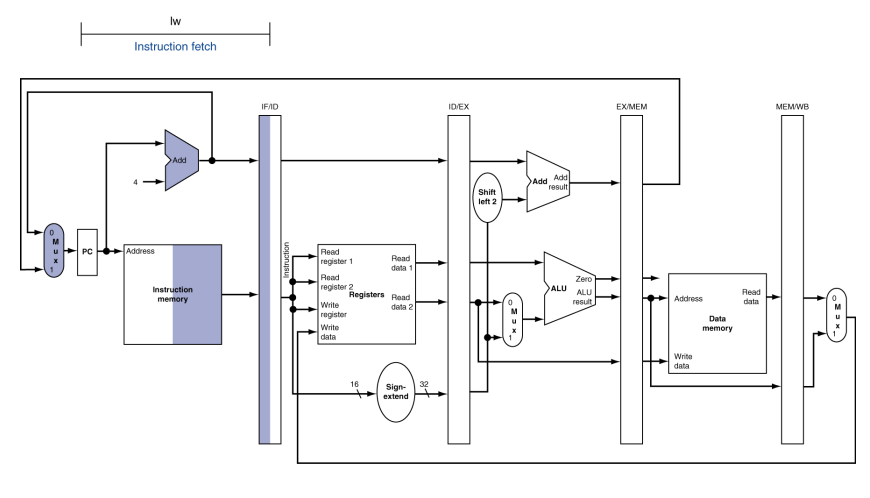

이렇게 데이터패스를 구축하고 Pipeline 시켰을 때 문제가 뭐가 있을까?

단일 사이클 환경에선 한명령어가 끝난 다음 다음 명령어가 실행되었으므로, 각 메모리 레지스터파일 등이 갖고 있는 정보가 하나의 명령어에 관한 것이었기 때문에 정보를 별도로 저장할 필요가 없었다.

그러나 파이프라이닝 환경에서는 레지스터 파일에 들어오는 정보가 다음의 명령어의 레지스터 정보로 계속 바뀌고, WB할 때, 레지스터 파일의 write address주소가 이미 업데이트 되어버린 상태이다.

즉 이제 각 stage의 상태를 저장하기 위한 장소가 필요한데 이를 파이프라인 레지스터라고 한다.

이렇게 4개의 pipeline 레지스터를 배치함으로써 각 stage의 상태를 저장하고, 다음 cycle때 이 정보가 다음 stage로 전달되게 된다.

참고로 PC 레지스터를 포함하여 5개까지 파이프라인 레지스터라고 하기도 한다.

Load word 되는 과정을 pipeline을 통해서 알아보자

1. 명령어 인출 : PC에 있는 주소를 통하여 메모리로부터 명령어를 읽어오고 이를 IF/ID 파이프라인 레지스터에 저장한다. 이때, PC+4값도 저장해주는데, beq같은 명령어에 PC+4의 값이 필요하므로 같이 해당 정보를 레지스터에 저장하여 보내주는 것이다.

2. 명령어 해독 및 레지스터 파일 읽기 : IF/ID 파이프라인 레지스터로부터 정보를 받아와서 레지스터파일로부터 읽은 정보와 상수필드의 값,PC+4정보를 ID/EX 파이프라인 레지스터에 전달한다. 이때, 그림 상엔 없지만 Contol unit으로 부터 받은 Control Signal도 같이 전달된다.

3. 실행 또는 주소 계산 : ID/EX 파이프라인 레지스터로부터 값들을 받아와서 계산해준다. 이때 받은 Control Signal로 ALUSrc 신호를 통해 rt레지스터에 있는 값이 아닌 상수필드에 있는 값과 rs필드에 있는 값을 더해준다. 이후 계산한 결과를 EX/MEM에 전달해준다. 이때 rt 필드의 값도 같이 전달해준다.

4. 메모리 접근 : ALU로부터 받은 결과 값을 주소로 이용해 해당 주소에 있는 값을 읽고 MEM/WB 레지스터로 보내준다.

5. 쓰기 : 이제 중앙에 있는 레지스터 파일에 읽어온 값을 써준다. 이때, 레지스터 파일의 write register 주소는 다른 명령어로부터 받아온 값일 것이다. 이를 위해 ID stage부터 rt필드의 값을 파이프라인 레지스터에 계속 저장하여 보내주고 WB할때 해당 정보를 이용하여 해당 레지스터에 값을 써준다.

5개의 명령어가 실행되는 파이프라인 다이어그램을 보면 다음과 같다.

파이브라인 레지스터를 배치함으로써 파이프라인stage를 서로 고립시켜 다른 명령어를 작업할 수 있게끔 한다.

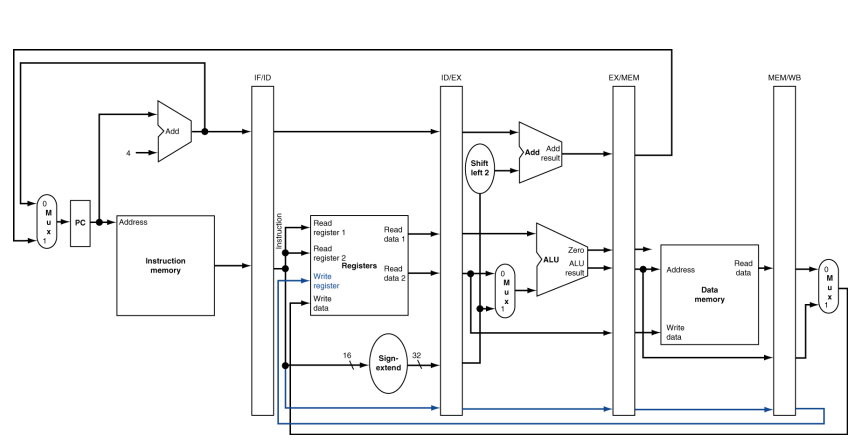

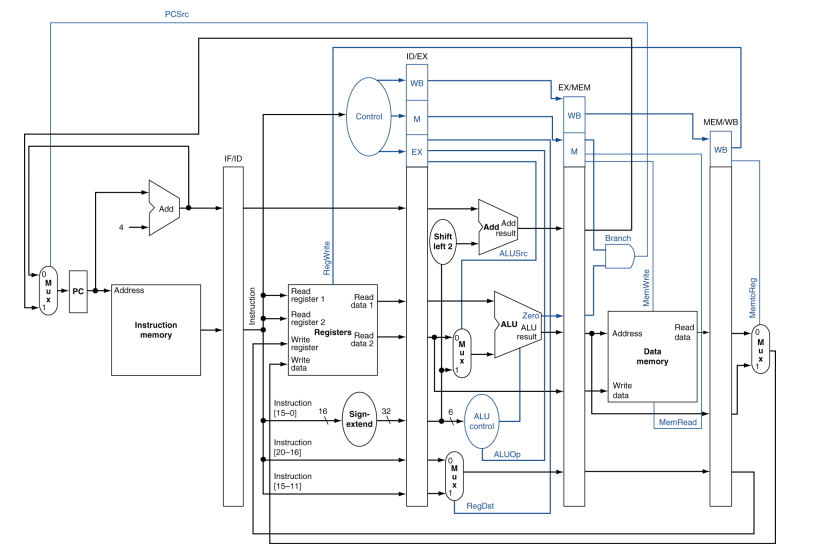

Pipelined Control

Single cycle에서 Conrol 신호가 있었는데 이는 파이프라인에서도 똑같다.

그림과 같이, 총 9bit가 추가로 들고, 해당 stage에서 필요한 conrol signal을 사용하고 나면, 다음 stage에서는 해당 control 신호가 필요 없기 때문에 추가로 보내지 않는다.

즉, ID/EX에선 추가로 9bit가 필요하고, EX/Mem에선 5bit, MEM/WB에선 2bit가 필요하게 된다.

컨트롤 신호를 포함한 데이터 패스는 다음과 같다.

각 파이프라인 레지스터에는 얼마 만큼의 bit가 필요한지 알아보자

- PC - 32bit

- IF/ID - 32(명령어) + 32(PC+4)

- ID/EX - 9(control) + 32(rs레지스터 값) + 32(rt레지스터 값) + 32(상수 필드 sign extend된 값) + 32(PC+4) + 5(rt주소) + 5(rd 주소)

- EX/MEM - 5(control) + 1(zero bit) + 32(연산 결과) + 32(Branch target address)+ 32(rt레지스터 값) + 5(rt or rd 주소)

- MEM/WB = 2(control) + 32(메모리에서 읽은 주소) + 32(ALU 연산 결과) + 5(rt or rd 주소)

각 파이프라인 레지스터는 다음과 같이 bit가 필요하다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [Chapter 4.9 컴퓨터 구조 및 설계] Control Hazards와 Prediction (0) | 2022.07.22 |

|---|---|

| [Chapter 4.8 컴퓨터 구조 및 설계] Structure Hazards, Data Hazard(Fowarding) (0) | 2022.07.21 |

| [Chapter 4.6 컴퓨터 구조 및 설계] 파이프라이닝에 대한 개관 (0) | 2022.07.20 |

| [Chapter 4.5 컴퓨터 구조 및 설계] 데이터패스 control unit, control signal (0) | 2022.07.19 |

| [Chapter 4.4 컴퓨터 구조 및 설계] ALU 하드웨어 (0) | 2022.07.19 |