본 정리는 CS422-컴퓨터 구조 및 설계 : 하드웨어/소프트웨어 인터페이스. David A. Patterson, 존 헤네시 책을 바탕으로 하고 있음을 미리 알립니다.

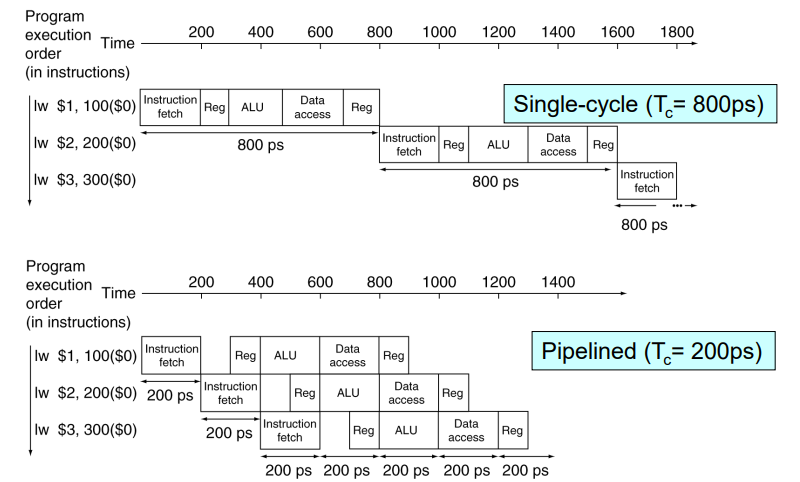

지금까지 구현한 단일 사이클 구현은 이러한 설계에서 모든 명령어에 대해 가장 긴 시간이 걸리는 load word(데이터패스를 그려보면 명령어 메모리, 레지스터 파일, ALU, 데이터 메모리, 레지스터 파일의 5 과정을 거치므로 시간이 가장 오래 걸린다.)를 기준으로 똑같은 클럭 사이클을 갖는다.

이렇게 구현하면, CPI (Clock cycle per Instruction)는 한명령어에 한 번의 사이클만 들기 때문에 1밖에 되지 않지만, 클럭 사이클이 매우 길기 때문에 전체 성능이 좋지 않다.

참고: https://developbear.tistory.com/33?category=1016411

[Chapter 1.2 컴퓨터 구조 및 설계] 컴퓨터의 성능과 CPU Time

본 정리는 CS422-컴퓨터 구조 및 설계 : 하드웨어/소프트웨어 인터페이스. David A. Patterson,존 헤네시 책을 바탕으로 하고 있음을 미리 알립니다. 성능 어떤 컴퓨터가 다른 컴퓨터보다 성능이 좋다는

developbear.tistory.com

심지어 load word 명령어 이외의 명령어조차 느려지게 된다.

이는 자주 생기는 일을 빠르게 하라는 설계 원칙을 위반한다.

이를 해결하기 위해 파이프라이닝 기법이 나왔다.

파이프라이닝

파이프라이닝이란 조립 라인처럼 여러 명령어의 실행이 중첩되는 구현 기술이다.

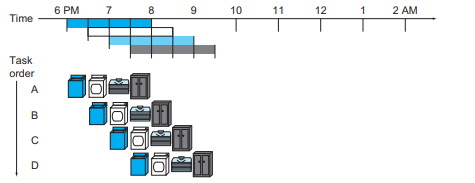

세탁을 예를 들어서 생각해보자

다음과 같이 다른 자원을 사용하더라도, 한 작업이 모두 끝난 다음에 다음 작업을 수행한다고 가정해보자.

이는 우리가 지금까지본 단일 사이클과 비슷하다.

그러나 위와 같이 한 자원을 쓰고 있지 않을 때는 쓰지 않고 있는 자원을 중첩하여 수행하여 훨씬 효율적으로 일을 빨리 끝낼 수 있다. 이는 파이프라인 방식과 매우 유사하다.

파이프 라인의 특징

- 파이프 라인은 단일 작업에 대한 속도를 늘리진 않는다. 전체 작업에 대한 단일 시간 내 처리량(throughput)이 좋아진다.

- 파이프 라인의 속도는 가장 느린 파이프라인 stage에 의해 결정된다. (가장 느린 stage를 클럭 사이클로 해야 파이프라인을 중첩시키고 모든 작업이 다 끝났을 때 다음 사이클을 실행할 수 있다.)

- 여러개의 업무가 동시에 다른 자원을 사용되며 실행된다.

- 속도의 향상은 pipe line stage 수와 같다.

- 파이프라인 stage의 불균형한 길이는 속도 향상을 늦춘다.

- 파이프라인을 채우는 데 걸리는 시간과 마지막에 전부 배출해내는데 걸리는 시간이 속도 향상을 늦춘다.

- 서로 의존성이 생긴다.

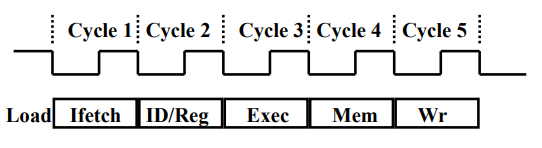

MIPS의 파이프라인은 다음의 5가지 stage를 갖는다.

- IF: Instruction fetch from memory

- ID: Instruction decode & register read

- EX: Execute operation or calculate address

- MEM: Access memory operand

- WB: Write result back to register

Single cycle vs Multiple Cycle vs Pipeline

- Single cycle : 우리가 지금까지 봐왔던 cycle이다. 가장 길게 걸리는 명령어를 기준으로 clock cycle time이 결정되고, 이보다 짧게 걸리는 명령어가 있더라도 모든 명령어가 결정된 clock cycle time의 시간이 걸린다.

- Multiple Cycle : pipeline처럼 stage를 나누어 가장 긴 시간이 걸리는 stage를 기준으로 clock cycle time을 결정한다. 그러나 다른 점은 병렬적으로 수행되는 것이 아니라 순차적으로 수행되고, WB stage를 거치지 않으면 해당 cycle을 생략하고 실행된다.

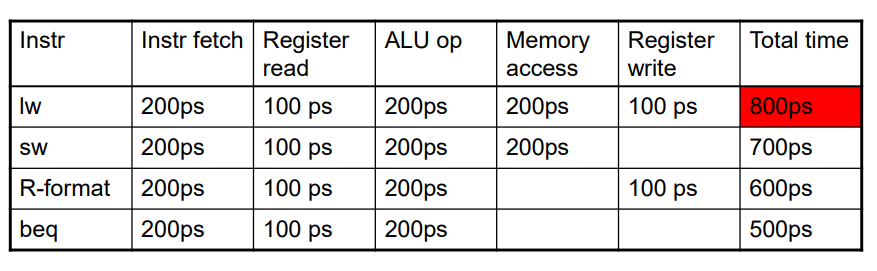

각 명령어의 stage가 다음과 같이 시간을 차지한다고 가정하고, 성능을 비교해보자.

이상적인 속도 향상은 stage가 5개 이므로 5배가 되어야한다. 그러나 지금은 속도 향상이 4배가 되었다. 이는 unbalanced 된 stage time 때문이다.

만약 모든 명령어가 다 200ps된다고 생각하면 Single-cycle은 1000ps가 걸리게 되어 이상적인 5배의 속도 향상을 볼 수 있다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [Chapter 4.8 컴퓨터 구조 및 설계] Structure Hazards, Data Hazard(Fowarding) (0) | 2022.07.21 |

|---|---|

| [Chapter 4.7 컴퓨터 구조 및 설계] Pipelined Datapath, Pipelined Control (0) | 2022.07.20 |

| [Chapter 4.5 컴퓨터 구조 및 설계] 데이터패스 control unit, control signal (0) | 2022.07.19 |

| [Chapter 4.4 컴퓨터 구조 및 설계] ALU 하드웨어 (0) | 2022.07.19 |

| [Chapter 4.3 컴퓨터 구조 및 설계] processor datapath와 레지스터 파일 (0) | 2022.07.19 |