본 정리는 CS422-컴퓨터 구조 및 설계 : 하드웨어/소프트웨어 인터페이스. David A. Patterson, 존 헤네시 책을 바탕으로 하고 있음을 미리 알립니다.

멀티코어 멀티프로세서는 여러 개의 프로세서가 하나의 칩안에 들어 있는 것을 말한다.

메모리 공간은 한정되어있고 이러한 프로세서들은 공통의 실제 주소공간을 공유한다.

두 개의 서로 다른 프로세서가 각자 자신의 캐시를 통하여 메모리에 접근하게 되고, 주의하지 않으면 두 개의 다른 값을 갖게 된다.

멀티코어 멀티프로세서를 사용하는 것은 캐시 일관성 문제를 야기한다.

캐시 일관성

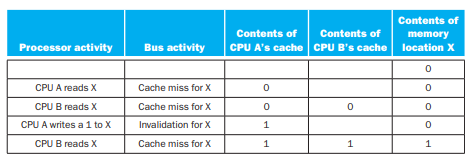

두 CPU가 메모리를 공유한다고 가정하고 위의 step이 순서대로 일어난다고 생각해보자.

같은 X라는 데이터를 읽어왔는데, CPU A에서는 X에 데이터를 쓰기 때문에 CPU A캐시에서는 X를 1이라고 인식하지만, CPU B에서는 여전히 X를 0이라고 인식하는 문제가 생긴다.

이러한 문제를 캐시 일관성 문제라고 한다.

일관성과 정합성

일관성은 읽기에 의해 반환되는 값이 어떤 값들인지 정의한다.

정합성은 쓰여있는 값이 읽기에 의해 언제 반환되는지를 결정한다.

아래와 같은 조건이라면 메모리 시스템은 일관적이다.

- P writes X; P reads X; 이때 쓰기와 읽기 사이에서 어떠한 다른 프로세서도 X에 관여하지 않았다면, 항상 P에 의해 쓰인 값을 반환한다.

- P1 writes X; P2 reads X; 이때 두 작업이 시간적으로 분리되어 있으며 두 동작 사이에 X에 대한 다른 쓰기 작업이 없었다면 쓰인 값이 반환된다. 위의 캐시 일관성 예시 문제에서는 CPU B의 캐시의 값을 바꾸는 절차가 필요하다.

- P1 writes X; P2 writes X; 동일한 위치에 두 개의 프로세서 쓰기를 수행한 경우 모든 프로세서에 동일한 순서로 보이게 한다. 이를 쓰기 순서화라고 한다.

일관성을 유지하기 위해 캐시는 공유된 데이터의 이동과 복사 기능을 제공해준다.

- 복사 : 공유된 데이터가 동시에 읽힐 때, 캐시는 지역 캐시 안에 복사본을 만든다. 복사는 공유 데이터 접근 시 대기시간과 읽기 경쟁을 감소시킨다.

- 이동 : 데이터는 지역 캐시로 이동될 수 있다. 이동은 먼 곳에 위치한 공유 데이터에 접근할 때 발생하는 지연과 공유 메모리 요청에 따른 대역폭을 줄여준다.

캐시 일관성 유지 프로토콜 - 스누핑

이러한 일관성을 유지하기 위해 도입한 하드웨어 프로토콜을 캐시 일관성 유지 프로토콜이라고 부른다.

이때, 가장 널리 사용되는 캐시 일관성 유지 프로토콜은 스누핑(snooping)이다.

모든 캐시는 실제 메모리 블록으로부터의 데이터 복사본을 가지고 있고, 블록의 공유 상태에 대한 복사본도 가지고 있더, 그러나 중앙에서 관리되는 상태는 유지하지 않는다. 캐시들은 전송 매체(버스 or 네트워크)를 통하여 모두 접근 가능하다.

그리고 모든 캐시 제어기들은 버스 또는 스위치 접근에 의해 요청된 블록의 복사본을 가지고 있는지 없는지를 확인하기 위하여 매체를 감시(snoop)한다.

이러한 프로토콜은 쓰기 작업 시 다른 캐시에 있는 복사본들을 무효화 하기 때문에 쓰기 무효화 프로토콜이라고 부른다.

다른 프로세서에서의 읽기 작업 후에 쓰기 작업이 일어나는 경우를 예를 들어보자.

쓰기 작업은 배타적 접근을 요구하기 때문에 다른 프로세서에서의 쓰기 작업에 잡혀 있는 모든 복사본들을 무효화 시킨다. 즉, 일기 작업이 일어날 때, 캐시에서 실패가 되고, 캐시는 데이터의 새로운 복사본을 가져와야만 한다.

쓰기 작업이 진행될 때는 배타적 접근 이므로 다른 프로세서에서 쓰는 것을 방지하고, 만약 동시에 쓰려한다면 둘 중 하나의 작업은 경쟁에서 이기게 되고, 다른 프로세서의 복사본은 무효화된다.

그러므로 이 프로토콜은 쓰기 순서화를 따른다.

위의 예시와 독같이 진행했을 때 스누핑 프로토콜을 이용하면 다음과 같이 될 것이다.

일관성 Miss

말 그대로 일관성이 유지되지 않는 것을 말한다.

Coherence miss는 한 블럭의 데이터를 멀티 프로세서가 공유할 때 나타난다.

이떄 블록의 공유는 두가지로 나눌 수 있다.

- True sharing : 하나의 프로세서에서 생성된 word가 다른 프로세서에 의해 사용되는 공유

- False Sharing : 두 개의 연관되지 않은 word가 같은 블록에 위치하고 있을 때, 다른 프로세서가 한 word가 직접적으로 필요하지 않더라도 나머지 하나의 word가 필요해 전체 블록을 공유하는 것

True Sharing Miss

True Sharing에서 miss가 나는 경우는 한 프로세서가 word에 쓰기하여 block을 invalidated시키고, 다른 프로세서가 해당 word에 읽기 요청을 하는 경우 cache miss가 발생하는 경우이다.

False Sharing Miss

Core1 이 A에 접근하는 동안 블록 전체가 invalidated되기 때문에 Core2가 A가 아니라 B에 접근할 때도 cache miss가 발생하여 miss rate가 증가한다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [Chapter 5.7 컴퓨터 구조 및 설계] 메모리 계층을 위한 공통 구조 (0) | 2022.07.31 |

|---|---|

| [Chapter 5.6 컴퓨터 구조 및 설계] TLB (0) | 2022.07.31 |

| [Chapter 5.5 컴퓨터 구조 및 설계] 가상 메모리와 페이지 부재 (0) | 2022.07.30 |

| [Chapter 5.4 컴퓨터 구조 및 설계] 캐시의 성능, Multilevel Caches, set associative cache (0) | 2022.07.29 |

| [Chapter 5.3 컴퓨터 구조 및 설계] 캐시 참조 실패와 성공의 처리 (0) | 2022.07.28 |