본 정리는 CS422-컴퓨터 구조 및 설계 : 하드웨어/소프트웨어 인터페이스. David A. Patterson, 존 헤네시 책을 바탕으로 하고 있음을 미리 알립니다.

TLB를 이용한 빠른 주소 변환

페이지 테이블은 메인 메모리에 저장되기 때문에, 프로그램에 의한 모든 메모리 접근은 최소한 두 번 필요하게 된다.

- 프로세스 테이블 접근

- 얻은 physical address를 이용한 메모리 접근

그러나 페이지 테이블에 접근하는 것 또한 참조의 지역성이 높다.

즉, 한번 참조한 테이블은 다시 참조될 가능성이 크다.

그래서 페이지 테이블에 접근하는 것을 피하기 위해 최근에 사용된 변환을 보관하고 있는 캐시인 Translation Look-aside Buffer(TLB)를 이용한다.

TLB에는 Virtual page number가 있어 가상 페이지 번호의 일정 부분을 갖고 있고, 이에 대응하는 실제 메모리 주소를 갖고 있다.

TLB는 캐시이기 때문에 다른 캐시들과 마찬가지로 fully associative, set associative, direct mapped의 구조를 가질 수 있다. (보통 다른 캐시보다 작아서 cache access time이 훨씬 조금 든다.)

TLB는 크기가 작고 모든 Page를 담고 있는 것이 아니기 때문에 TLB Miss가 일어날 수도 있다. (page table보다 빈번히 일어난다)

TLB 실패 시 일어나는 과정

- 우선 TLB에는 없지만 현재 메모리에 있는 상태일 수도 있기 때문에 Page Table을 통해 현재 메모리에 있는지 확인한다.

- 메모리에 있을 때,

- 해당 변환(page)을 TLB에 다시 적재하고 참조를 시도한다. -> 10~100 cycle 정도 걸린다

- 메모리에 없을 때,

- 예외를 사용하여 운영체제로 하여금 처리하게 한다. -> 1000000 cycle 정도 걸린다.

- 메모리에 있을 때,

TLB Miss Handler

PTE(page table entry)까지 참조하여 page가 현재 메모리에 있는지 없는지 확인한다.

메모리에 있다면 PTE(page table entry)를 복사하여 TLB에 적재한다.

없다면 Page Fault Handler를 호출한다.

Page Fault Handler

PTE의 valid bit이 0 임을 확인한다.

disk로부터 원하는 page를 가져온다

메모리가 꽉 차 있다면, LRU 전략을 사용하여 페이지를 대체한다.

페이지를 메모리와 page table에 업데이트한다.

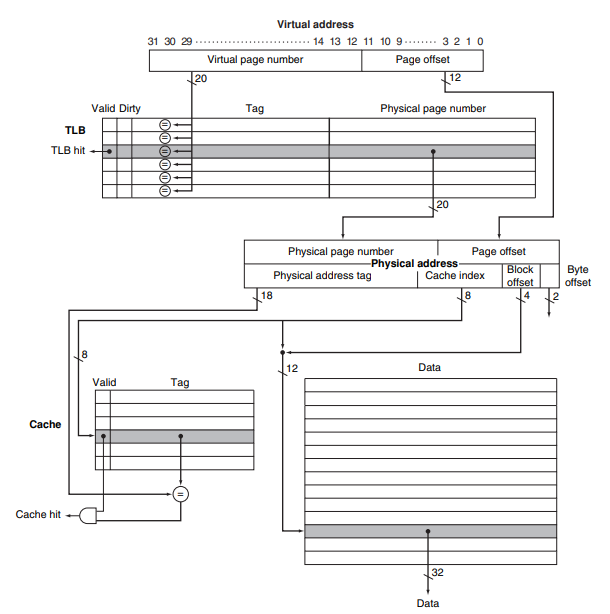

지금까지 배운 TLB와 cache가 상호작용하는 구조이다.

먼저 TLB를 통해 페이지를 찾을 수 있는지 확인한다.

만약 페이지를 찾을 수 있다면 더 빠른 캐시에 접근하여, 캐시에 데이터가 있는지 확인하여 cache hit 혹은 cache miss를 진행한다.

즉, TLB hit이라고 무조건 메인 메모리에서 데이터를 가져오는 게 아니라 더 빠른 캐시까지 접근하여 cache에서 데이터를 가져올 수 있는지 확인하고 없다면 cache에도 데이터를 업데이트해준다.

cache가 Page Table의 부분집합 / TLB가 Page Table의 부분집합임을 상기하면서 다음 표를 채워보기를 바란다.

(참고) 가상 메모리를 사용하면서 가상 캐시를 사용하지 않는 이유

캐시도 메모리처럼 가상 주소로 접근되고, 페이지가 프로그램들 사이에 공유될 때 동의어 문제가 발생할 수도 있기 때문이다.

동의어 문제란? 같은 객체가 두 개의 주소에 의해 접근되는 상황. 같은 실제 페이지가 두 개의 가상 주소가 존재하는 가상 메모리에서 발생할 수 있다.

이러한 모호함은 페이지 내의 워드가 각각 다른 가상 주소로 대응되는 두 개의 다른 캐시 블록에 들어갈 수 있기 때문에 문제를 발생시킨다.

이러한 문제의 타협으로 캐시는 가상 주소로 인덱스 되고, 실제 주소의 태그를 사용하는 방식을 사용할 수 있다.

이러한 설계 방식은 지금껏 봐온 단순한 캐시의 단순한 구조에 힘입어 가상 주소 캐시보다 더 좋은 성능을 낸다

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [Chapter 5.8 컴퓨터 구조 및 설계] 병렬성 메모리 계층구조에서의 캐시 일관성 (0) | 2022.08.01 |

|---|---|

| [Chapter 5.7 컴퓨터 구조 및 설계] 메모리 계층을 위한 공통 구조 (0) | 2022.07.31 |

| [Chapter 5.5 컴퓨터 구조 및 설계] 가상 메모리와 페이지 부재 (0) | 2022.07.30 |

| [Chapter 5.4 컴퓨터 구조 및 설계] 캐시의 성능, Multilevel Caches, set associative cache (0) | 2022.07.29 |

| [Chapter 5.3 컴퓨터 구조 및 설계] 캐시 참조 실패와 성공의 처리 (0) | 2022.07.28 |